Yasunao Tone

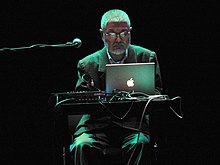

Yasunao Tone (刀根 康尚, Tone Yasunao, born 1935) is a multi-disciplinary artist born in Tokyo, Japan and working in New York City. He graduated from Chiba University in 1957 with a major in Japanese Literature. An important figure in postwar Japanese art during the sixties, he was active in many facets of the Tokyo art scene. He was a central member of Group Ongaku and was associated with a number of other Japanese art groups such as Neo-Dada Organizers, Hi-Red Center, and Team Random (the first computer art group organized in Japan).[citation needed] Tone was also a member of Fluxus and one of the founding members of its Japanese branch.[1] Many of his works were performed at Fluxus festivals or distributed by George Maciunas’s various Fluxus operations. Relocating to the United States in 1972, he has since gained a reputation as a musician, performer and writer working with the Merce Cunningham Dance Company, Senda Nengudi, Florian Hecker, and many others.[2][3] Tone is also known as a pioneer of “Glitch” music due to his groundbreaking modifications of compact discs and CD players.

Early life in Tokyo

[edit]While in high-school Tone became interested in Japanese Avant-Garde poetry and prose of the 1920s and 30s.[4] After entering the Literature program at Chiba National University, where he was enrolled from 1953-1957, Tone’s interest in literature expanded to a more general interest in the modernism of the interwar period.[4] During this time, Tone was particularly influenced by Assistant Professor Tsuneyoshi Shigenobu and the instructor Isamu Kurita.[4] Under Shigenobu’s guidance, Tone and his classmates translated Maurice Blanchot’s La Part du feu over a two-year period. Kurita, on the other hand, taught Tone about Bataille as well as introduced him to critics and poets of his own generation such as Yoshiaki Tōno, Kōichi Iijima and Makoto Ōoka.[4] Tone, meanwhile, continued to seek out prewar Japanese avant-garde culture in journals such as “Shi to Shinron,” “Ge.Gjgjgam.Prr.Gjmgem,” “Bara●Majutsu●Gakusetsu,” and “Fukuikutaru Kafu-yo” and through the work of Tomoyoshi Murayama and his Mavo group.[5] Tone then wrote his thesis on Dada and Surrealism, interviewing many of the prominent figures of the 20th century avant-garde in Japan in the process such as Katsue Kitazono, Shūzō Takiguchi, Kōichi Kihara and Sansei Yamanaka.[5][6]

Group Ongaku and Other Early Artistic Activity

[edit]In the late 1950s, Shūko Mizuno, Tone’s classmate at Chiba University enrolled at the Tokyo National University of Fine Arts and Music (Tokyo Geijutsu Daigaku, abbrev. Geidai) and began musically improvising with classmate Takehisa Kosugi.[7] Kosugi played a tape for Tone and asked him to join their sessions.[7] Tone was affected by Kosugi’s gesture, who seemed to show no regard for Tone’s lack of formal musical training.[7] He joined their group, buying a saxophone from Kosugi and a Sony open reel tape recorder.[7] Mieko Shiomi, Genichi Tsuge, Mikio Tohima and Yumiko Tanno also joined, making Tone the only member not enrolled at Geidai. Mizuno’s house became an important meeting place for the group.[7] The group’s experimental endeavors were further informed by the young ethnomusicologist Fumio Koizumi, who became a part-time faculty member at Geidai in September 1959.[7] As historian William Marotti describes, “The different ‘ethnic’ instruments were each bound to a complex performance tradition outside of a western orchestral frame—and thus provided a variety of rich alternatives to the latter’s conceptual dominance of music with its particular, narrow, and oppressive systematicity.”[7] Tone recounts influence by Noh music, Indian music, Jazz musicians like Ornette Coleman and Eric Dolphy and Kabuki music, among others.[8] According to his own account, Tone saw music as lagging behind the experimentation present in other art forms of the time and therefore providing a rich ground for the transformative capacity of art.[9]

Tone also wrote about the group, first in August of 1960 where he emphasized the role of chance and their endeavoring in “an experiment concerning an absolutely new music.”[9] At this time, the group also decided upon its name as “Group Ongaku,” “ongaku” meaning “music” in Japanese.[10] As Marotti points out, this emphasis on chance was part of Tone's and the group’s exploration of a Surrealist-inspired automatism in opposition to artistic egoism.[11] The group’s improvisational approach to collective art making therefore had wider theoretical consequences for the social import of art. Inseparable from this work is its contextualization within the massive protests against the renewal of U.S.-Japan Security treaty (abbreviated as Anpo), as seen in their performance from the van of Tone’s family’s business during the Anpo protests.[12]

Among his early influences, Tone has cited Concrete Music, John Cage’s experiments with sound, Jackson Pollock’s action painting, and Art autre/Art informel.[13] A former literature major, Tone became a fixture within the Japanese contemporary art scene. Tone was involved with the Neo Dadaism Organizers group, attending and sometimes participating in their events such as those conducted at Masunobu Yoshimura’s “White House” in Shinjuku,[14] In the early sixties he became involved with the international Fluxus movement. For example, his 1961 score Anagram for Strings was published and distributed by George Maciunas’s Fluxus Editions in 1963.[15] This work was Tone’s first graphic score, and it was performed during the first Fluxus festival, a 1962 tour around Europe.[16] Dasha Dekleva describes the score, writing that it “is populated with small white and black circles and dots, and with random whole numbers (positive and negative) along the top and left edges. The realization of the piece involves drawing a line across the score and using basic arithmetic calculations that determine how a series of downward glissando is to be performed.”[17] Among other shorter scores, Anagram for Strings was translated to English by Yoko Ono.[15] In another 1961 work, Days, Tone recorded himself counting to past one hundred at a low volume. He then played the recording back at a high volume, re-recording it.[15] This process was repeated multiple times until the distortion has completely obscured the sound to unintelligibility.[15] In 1961 Tone also produced Geodessy For Piano in which he “experimented with the inevitable indeterminacy of a precise execution of sounds,” according to art historian and curator Alexandra Munroe.[18] In this work, Tone stood elevated on a ladder above an open piano. He then took various handheld objects such as a tennis ball or cork and dropped them one-by-one onto the exposed strings.[18] Tone would also modify the method by ascending or descending the ladder to increase or decrease the distance from which the objects were dropped.[18]

1962 saw a multitude of notable events in Tone’s oeuvre, including his first solo concert “One-man Show by Composer” in February.[17] The concert occurred at the former Minami Gallery space with assisting performers seated on tatami mats on the floor.[17] Compositions performed here include Anagram, Smooth Event, Silly Symphony and Drastic, in which the performer took a large amount of laxatives and performed on the drums until they had to use the bathroom.[15] 1962 also saw the Yamanote Line Incident, by Natsuyuki Nakanishi, Jirō Takamatsu and Hiroshi Kawani. Tone and Kosugi also participated, although they performed on a different spot along the circular loop of the Yamanote train line than the other group.[19] Tone and Kosugi were supposed to meet up with the primary group at Ikebukuro, but the primary group ended their performance prematurely when Nakanishi became too nervous to continue.[19] Tone and Kosugi, on the other hand, completed the circuit of the Yamanote line, playing mobile tape players so that the sounds from the tapes and the sounds from around the train lines intermingled.[19]

Tone’s first submission to the progressive Yomiuri Independent Exhibition, an annual exhibition that had become a hotbed of experimental artistic activity and discourse, also occurred in 1962. This submission was titled Tēpu Rekōdā (Tape Recorder).[20] The work was initially a reel to reel tape recorder which, after some uncertainty, he painted in hopes of making it a more acceptable submission to the art exhibition.[14] Unhappy with this, he placed this entire tape recorder inside of a big white cloth bag that belonged to Kosugi.[14] The result was an amorphous cloth form that would occasionally produce strange sounds on the thirty to forty minute loop.[21] The following year, the final year of the Yomiuri Independent, Tone produced Something Happened (1963).[22] Acquiring the stereotype mold of the Yomiuri newspaper (the exhibition sponsor) published that day, Tone rendered the news in plaster.[22] Other works from this period were more performative, such as Catch Water Music (1965), a collaboration with Tatsumi Hijikata, in which Tone threw water from a balcony onto the stage below.[23] Around this time Tone also frequented the events at the Sōgetsu Art Center. It was here that Tone met Nam June Paik, who had been working in Tokyo with Shūya Abe between Summer of 1963 and Spring of 1964.[24]

Criticism and theory

[edit]Tone was also a prolific and important writer and theorist of art. In his 1961 “Toward Anti-Music,” for example, he describes a progression in Western music from “musical tone” to “abstract music.”[25] From here is outlines its logical successor as “concrete music” in European musique concrète and American “indeterminate music,” invoking John Cage.[25] He writes, “They focused on concrete sonority (i.e., actual sound of instruments) in a rejection of the abstract musical tone.”[25] In conclusion he notes that while these developments have certainly inspired experimental music in Japan, Japanese artists must not assimilate concrete music as “novel techniques.”[25] “[W]e are making a fresh start after realizing that Japanese ‘avant-garde’ music always appropriated new Western trends only to imitate their techniques,” he declares.[25] The text gives some insight into the aims of his concurrent activities with Group Ongaku activities that Tone and how they might diverge (through an emphasis on group improvisation, for example) from the European precedents of musique concrète and “indeterminate music.”

Tone’s influence through his writing and theory may also be detected when art historian Reiko Tomii credits him with helping to solidify the term “gendai bijutsu” (contemporary art) to indicate the new idiom of postwar art in Japan as distinct from other terms such as “kindai bijutsu” (modern art) or “zen’ei” (avant-garde).[26] This articulation of a new idiom received textual form in “Chronology: Five Decades of Contemporary Art, 1916-1968” in 1972. For this text, Tone, along with Naoyoshi Hikosaka and Yukio Akatsuka, compiled a history of Japanese contemporary art, published in Bijutsu Techo.[27] Tone was an important friend and influence upon Hikosaka, an important progenitor of conceptualism in Japan. Tone’s role as an influential theorist for young Japanese contemporary artists can be observed in his relationship Hikosaka more generally, to whom he introduced the works of Fluxus and John Cage as well as the philosophy of Edmund Husserl.[28] It was Tone who also suggested that Hikosaka use latex as the material for his important 1970 Floor Event piece instead of the conventional art material of plaster, and who assisted in the work by pressing the shutter button on the 35 millimeter camera as Hikosaka brushed the latex over the floor of his home.[29] Tone was one of the five original artists of Hikosaka’s “Bikyōtō Revolution Committee,” a continuation of “Bikyōtō,” a radical, leftist student protest group at Tama Art University.[29]

In 1970 Tone compiled and published a book of his writing titled Gendai geijutsu no isō.[15]

Jury Event: Tone Prize Exhibition

[edit]In September 1964, Tone published an ad in “Ongaku Geijutsu” magazine that read, “Call for Entries: 1st Tone-Prize Composition.” Details read:

“Tone Prizes are given to all entries.

Deadline: October 1.

Certificates will be mailed in lieu of official announcement in early October.

There is no restriction on form or content. However, phenomena will not be accepted for they are impossible to present; instead please submit texts, etc. For further details, please contact: Yasunao Tone, 11 Asakusa Shōtenchō, Taitō-ku, Tokyo.

Announcement of Prizes

Works that receive Tone Prizes automatically qualify for the following individual prizes, which will be presented at a concert as Sogetsu Hall in late November.

Prizes include: Kosugi Prize, Ichiyanagi Prize, Okuyama Prize, Ono Prize, Akasegawa Prize, Nakanishi Prize, Takiguchi Prize, Takeda Prize, Ishizaki Prize, Shinohara Prize, Kobayashi Prize, Hijikata Prize, etc.

Performed and juried by: Kosugi Takehisa, Ichiyanagi Toshi, Okuyama Jūnosuke, Yoko Ono, Akasegawa Genpei, Nakanishi Natsuyuki, Takiguchi Shuzo, Takeda Akimichi, Ishizaki Koichiro, Shinohara Ushio, Hijikata Tatsumi, etc.

Cocurrence [sic] event 1964 Tokyo”[30]

The exhibition was conceived of Tone in response to the closure of the Yomiuri Independent, which was, according to Tomii, “the principle forum of anti-Art” and whose closure “prompted discussion of the dependency of vanguard artists on the corporate-sponsored ‘independent.’”[31] One entry to the Tone Prize Exhibition was Hi-Red Center’s canonical Cleaning Event (1964), a work that Tone participated in himself.[32]

Activity in the United States (1972-Present)

[edit]In 1972, Tone went to Mills College in Oakland to perform at the event “Repetition and Structure: Works of Yasunao Tone 1961-1964.”[15] What Tone had intended as a trip away from Tokyo, stopping in France, the Bay Area of California and New York, turned into a permanent residence when Tone decided to move to New York during that same trip.[33][15]

He was soon asked by David Behrman, director of the Merce Cunningham Dance Company, to do some composing for the following year’s season.[15] Tone created a piece for a two-day Cunningham event, Clockwork Video (1974), which used a pulley system to put in motion three turntables.[15][34] The first turned at a rate of one revolution per second, the second one per minute, and the last turntable one per hour.[15] He then placed a video camera on the turn table to capture the interior of the Cunningham Studio, which had a stage on one side and was mirrored on the other.[15] By placing the turn tables by the mirrored side, the footage captures the real space about half of the time while capturing its reflection for the other half.[15] The piece was accompanied by a text Tone wrote, compositing a Michel Foucault text on Gilles Deleuze and Tone’s own essay, “On Looking at Photography” (Shashin o miru koto ni tsuite).[15] A later version of the piece captured a female nude body in three sections: head, torso, and legs.[15] Projections of the respective sections rotated in intervals of one second, one minute and one hour, aligning at the completion of the hour.[15] Tone titled the work Clockwork Video à la Magritte.[15]

Another work prominently featured by Cunningham’s dance company was Geography and Music, performed from 1979 to 1987.[35] The work was commissioned by the American Dance Festival in Durham for Cunningham’s Roadrunners. The piece comprised a text, a notation for two amplified string instruments (derived from the tablature of ninth-century Chinese pipa music, and a gated audio system.[36] The work features the reading of passages from a late 10th century Chinese encyclopedia, describing various foreign places and people.[35]

Around this time, Tone became influenced by the work of East Asian Studies Scholar Shizuoka Shirakawa and his 1970 book Kanji in particular.[15] The book ethnographically traces the development of kanji characters.[15] Inspired by Jacques Derrida’s Of Grammatology, Tone began a process of translating kanji characters into sound.[15] This would prove to be a rich avenue for Tone’s experimentation in sound seen in works like Musica Iconologos and Musica Simulacra. Musica Iconologos (1993) converted two poems from the Shih Ching, China’s earliest poetic anthology, into sound.[37] Tone describes the process for producing his album Musica Iconologos as such: “first, the material source of the piece was derived from the poetic text of ancient China and each character of the text was converted into photographic images according to the ancient form of the Chinese characters which are closer to images than the modern form. I scanned the images and digitized them, thus the images were transformed simply into 0’s and 1’s. Then, I obtained histograms from the binary codes and had the computer read the histograms as sound waves; thus I got sound from the images.”[38] For example, “Solar Eclipse in October,” a poem composed of 262 early Chinese characters was turned into half an hour of experimental, chance-driven sound.[39] A similar method was employed for Musica Simulacra, debuted in 2003, which took the Man’yoshu collection of poems of the 7th and 8th centuries as its source material.[39] This particular project shows Tone’s multi-disciplinary concern in that it necessitated study of the obscure grammatology of the characters used (and sometimes invented) in the writing of the Man’yoshu anthology. With the original poem in mind, a relationship/pattern can be established between words and sound events. The repetition of a word is highlighted and traceable to an analogue waveform. Tone used these analog patterns, in addition to an artificial three-part structures, in 'Musica Iconologs' to reduce the listeners awareness off repetition.</ref> [40] His collaboration with Florian Hecker, Palimpsest, also transliterated Japanese Man'yōshū poems to sound.[41] As Tone notes, Musica Iconologos was developed specifically for the medium of compact disc. He writes, “I had received an offer to publish a CD; however, none of my pieces were suitable for recording. Certain formal elements of the pieces—spatial movement of sound, contrasting acoustic sound with amplified sound, and the use of visuals—made the pieces simply unrecordable. So I had to create something totally devoid of live performance, something that only the CD as a medium could produce.”[42] Because the musician’s hand is removed in Musica Iconologos, it can only be played and never performed. The compact disc as a means of dissemination and presentation were therefore integral to the production of the work itself.

Tone began manipulating compact discs to achieve uniquely mangled sounds in 1984.[43][44] Tone's CD-player-based works employ a process of "de-controlling" the device's playback so that it randomly selects fragments from a set of sound materials. Tone has stated that the error-correction functionality of modern CD players has made it hard to continue to use this technique and, for this reason, he continues to use older equipment.[43] Tone placed scotch-tape with small perforations on CD-roms of classical and popular music, causing the player to misread and information on the CD. The result was a unpredictable sonic distortion, uniquely generated by Tone’s intervention into the CD player’s specific technological mechanisms. Tone recounts discovering the process in an interview:

“I called my audiophile friend, who owned a Swiss-made CD player, and asked him about it. It was a simpler method than I suspected. I bought a copy of Debussy’s Preludes and brought it to my friend’s place. By his engineer friend’s suggestion, we simply made many pinholes on its of Scotch tape and stuck it on the bottom of a CD. I had many trials and errors. I was pleased [with] the result, because the CD player behaved frantically and out of control. [It] was a perfect device for performance.”[45]

In March 1986, Tone performed Music for 2 CD Players at the Experimental Intermedia Foundation in New York using this method.[46] According to Tone, Cage sat in the front row and “several minutes after the beginning of the performance he laughed loudly, over and over, until the end.”[46] After finishing the piece, Cage immediately came up to Tone and shook his hand.[47] The technique is also used in his 1997 album, Solo for Wounded CD.

Always active in the United States with avant-garde music artists, he has been awarded a CAPS Grant in multi-media, a 2004 Foundation for Contemporary Arts Grants to Artists Award, a New York State Council on the Arts commission grant for flutist Barbara Held, a National Endowment for the Arts grant for collaborative work with Blondell Cummings and Senga Nengdi, and a New York Foundation for the Arts Fellowship in performance/emerging forms. [citation needed] Tone has performed at the Kitchen, the Experimental Intermedia Foundation, P.S.1. Guggenheim Museum SOHO, and the Chicago Art Club among other notable venues.[48] He has been included in several institutional group exhibitions at venues such as The Whitney Museum of Art in New York, The Yokohama Triennale 2001 in Yokohama, and the Moderni in the Casselo Museum in Turin.[49] Music festivals featuring Tone include All Tomorrow’s Parties in London, Sonic Light in Amsterdam, and Spectacle Vivante at the Centre Pompidou in Paris.[49] In 1979 he was given the CAPS grant in multi-media and the Ars Electronica Golden Nica Prize in 2002.[50][49] In 2023 his work was celebrated with a mini-retrospective at Artists Space in New York City that was curated by Danielle A. Jackson.[51]

Selected discography

[edit]- (1993) Yasunao Tone : Musica Iconologos (Lovely Music) CD

- (1997) Yasunao Tone : Solo for Wounded CD (Tzadik) CD

- (2001) Yasunao Tone : Wounded Man'Yo #38-9/2001 (Alku) 3" CD

- (2003) Yasunao Tone : Yasunao Tone (Asphodel Records) CD

- (2004) Yasunao Tone & Hecker: Palimpsest (Mego) CD

- (2011) Yasunao Tone : MP3 Deviations #6+7 (Editions Mego) CD

- (2011) Yasunao Tone : MP3 Deviations #8 (Editions Mego) LP

- (2013) Yasunao Tone & Russell Haswell : Convulsive Threshold (Editions Mego) CD

- (2017) Yasuano Tone : AI Deviation #1, #2 (Editions Mego) LP =

See also

[edit]Bibliography

[edit]- Yasunao Tone: Noise Media Language. Ed. Brandon LaBelle (Los Angeles/Copenhagen: Errant Bodies Press, 2007). ISBN 0-9655570-8-1

- "Background Noise: Perspectives on Sound Art" by Brandon LaBelle (Continuum: New York, 2006), pp. 35–36, 39, 43, 45, 72, 153, 200, 218, 220-24, 241.

- "The Fluxus Reader" ed. Ken Friedman (John Wiley and Sons: New York, 1998).

- Caleb Stuart "Yasunao Tone's Wounded and Skipping Compact Discs: From Improvisation and Indeterminate Composition to Glitching CDs," Leonardo Electronic Almanac vol.10, no. 9, September 2002.

References

[edit]- ^ "Yasunao Tone – Blank Forms". Retrieved 2021-12-22.

- ^ Yasunao Tone Bio at Lovely Music http://www.lovely.com/bios/tone.html

- ^ "Brooklyn Museum". Brooklyn Museum. Retrieved 2021-12-22.

- ^ a b c d William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 17.

- ^ a b William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 18.

- ^ Hans Ulrich Obrist and Yasunao Tone, “Interview with Yasunao Tone,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 63-75, 63.

- ^ a b c d e f g William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 19.

- ^ Hans Ulrich Obrist and Yasunao Tone, “Interview with Yasunao Tone,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 63-75, 65.

- ^ a b William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 22.

- ^ William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 25.

- ^ William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 23.

- ^ William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 31.

- ^ William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 14.

- ^ a b c William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2006), pp. 13-33, 29.

- ^ a b c d e f g h i j k l m n o p q r s t "Sound Is Merely a Result: Interview with Tone Yasunao, 2". post. 2014-08-05. Retrieved 2021-11-13.

- ^ Dasha Dekleva, “In Parallel,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 39-54, 41.

- ^ a b c Dasha Dekleva, “In Parallel,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 39-54, 42.

- ^ a b c Alexandra Munroe, “A Box of Smile: Tokyo Fluxus, Conceptual Art, and the School of Metaphysics,” in Japanese Art After 1945: Scream Against the Sky (New York, NY: H.N. Abrams, 1994), 220.

- ^ a b c William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 32.

- ^ William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 29.

- ^ William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 29-30.

- ^ a b William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 30.

- ^ Dasha Dekleva, “In Parallel,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 39-54, 39.

- ^ Alexandra Munroe and Nam June Paik, “To Catch Up or Not to Catch Up with the West: Hijikata and Hi Red Center,” in Japanese Art After 1945: Scream Against the Sky (New York, NY: H.N. Abrams, 1994), 77.

- ^ a b c d e Alexandra Munroe, Japanese Art After 1945: Scream Against the Sky (New York, NY: H.N. Abrams, 1994), 376.

- ^ Reiko Tomii, “Historicizing ‘Contemporary Art’: Some Discursive Practices in Gendai Bijutsu in Japan,” Positions 12, no. 3 (2004): pp. 611-641, 622.

- ^ Reiko Tomii, “Concerning the Institution of Art: Conceptualism in Japan,” in Global Conceptualism (New York, NY: Queens Museum of Art, 1999), pp. 15-29, 22.

- ^ Reiko Tomii, “Infinity Nets: Aspects of Contemporary Japanese Painting,” in Japanese Art After 1945: Scream Against the Sky (New York, NY: H.N. Abrams, 1994), 319 n.48.

- ^ a b Tomii, Reiko. “The Impossibility of Anti: A Theoretical Consideration of Bikyōtō.” In The Anti-Museum: An Anthology, 474. Fribourg: Fri Art, 2017.

- ^ Yasunao Tone, translated by Reiko Tomii. Quoted from: Reiko Tomii, “Concerning the Institution of Art: Conceptualism in Japan,” in Global Conceptualism (New York, NY: Queens Museum of Art, 1999), pp. 15-29, 21.

- ^ Reiko Tomii, “Concerning the Institution of Art: Conceptualism in Japan,” in Global Conceptualism (New York, NY: Queens Museum of Art, 1999), pp. 15-29, 20.

- ^ Dasha Dekleva, “In Parallel,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 39-54, 47.

- ^ Dasha Dekleva, “In Parallel,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 39-54, 51.

- ^ Dasha Dekleva, “In Parallel,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 39-54, 52.

- ^ a b Dasha Dekleva, “In Parallel,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 39-54, 53.

- ^ Yasunao Tone and Judith Grossman, “Geography and Music: for Amplified String Music and Text,” Conjunctions 28 (1997): pp. 270-277, 272.

- ^ Federico Marulanda, “From Logogram to Noise,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 79-92, 82.

- ^ Hans Ulrich Obrist and Yasunao Tone, “Interview with Yasunao Tone,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 63-75, 72.

- ^ a b Tone book 82

- ^ Federico Marulanda, “From Logogram to Noise,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 79-92, 83.

- ^ Cisneros, R. Jiménez. (2009) BLACKOUT. Representation, transformation and de-control in the sound work of Yasunao Tone. Quaderns d'Àudio, Ràdio Web MACBA. Barcelona.

- ^ Federico Marulanda, “From Logogram to Noise,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 79-92, 91.

- ^ a b Cox, Christoph; Daniel Warner (2006). Audio Culture: Readings in Modern Music. Continuum International Publishing Group. pp. 341–347. ISBN 0-8264-1614-4.

- ^ "#1 BLACKOUT. Representation, transformation and de-control in the sound work of Yasunao Tone By Roc Jiménez de Cisneros | Radio Web MACBA | RWM Podcasts". rwm.macba.cat. Retrieved 2021-12-19.

- ^ Yasunao Tone, from a transcript of an interview published in Revue & Corrigée, No. 46 (2001) as quoted from: Caleb Stuart, “Damaged Sound: Glitching and Skipping Compact Discs in the Audio of Yasunao Tone, Nicolas Collins and Oval,” Leonardo Music Journal 13 (2003): pp. 47-52, 48.

- ^ a b Yasunao Tone, “John Cage and Recording,” Leonardo Music Journal 13 (2003): pp. 11-15, 12.

- ^ William Marotti, “Sounding the Everyday: the Music Group and Yasunao Tone’s Early Work,” in Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), pp. 13-33, 12.

- ^ Yasunao Tone and Robert Ashley et al., Yasunao Tone: Noise Media Language (Errant Bodies Press, 2007), 98.

- ^ a b c Yasunao Tone, “John Cage and Recording,” Leonardo Music Journal 13 (2003): pp. 11-15, 15.

- ^ Tone book 98

- ^ [1] Yasunao Tone: Region of Paramedia, Brooklyn Rail art review by Mark Bloch